# **Computer Architecture** Paul Mellies

Lecture 9 : Boolean Logic & Karnaugh Maps

## **Boolean Logic**

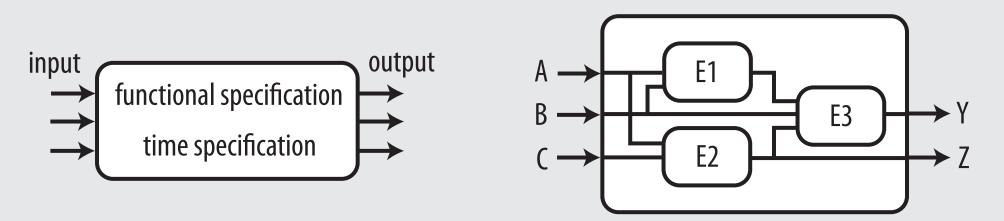

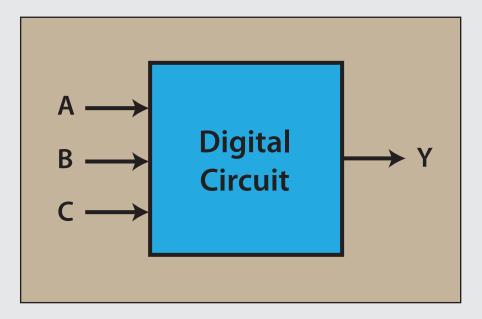

### **Circuit** (in digital electronics)

A circuit can be viewed as a black box with

- one or more discrete-valued input terminals

- one or more discrete-valued output terminals

- a functional specification describing the relationship between input and output

- a timing specification describing the delay

between inputs changing and outputs responding

Peering inside the black box, it is composed of

- nodes wires classified as input, output and internal

- elements themselves circuits

with inputs, outputs and specifications

Boolean algebra is based on three operations :

- conjunction :  $x \wedge y$

- disjunction :  $x \lor y$

- negation :  $\neg x$

and two constants :

- true : 1

- false : o

These operations and constants are required to satisfy a series of equations.

| Associativity :  | ( $x \wedge y$ ) $\wedge z$                      | = | $x \wedge$ ( $y \wedge z$ )            |

|------------------|--------------------------------------------------|---|----------------------------------------|

|                  | ( $x ee y$ ) $ee z$                              | = | x ee ( $y ee z$ )                      |

| Commutativity :  |                                                  |   |                                        |

| ·                | $x \wedge y$                                     | = | $y \wedge x$                           |

|                  | x ee y                                           | = | y ee x                                 |

| Distributivity : |                                                  |   |                                        |

|                  | $x \wedge$ ( $y \lor z$ )                        | = | ( $x \wedge y$ ) $ee$ ( $x \wedge z$ ) |

|                  |                                                  |   |                                        |

| Identities :     | $egin{array}{c} x \wedge 1 \ x ee 0 \end{array}$ | = | $oldsymbol{x}$                         |

|                  | $x ee \mathbf{o}$                                | = | x                                      |

| Annihilation :   |                                                  |   |                                        |

|                  | $r \wedge 0$                                     | _ | 0                                      |

$x \wedge \mathbf{o} = \mathbf{o}$

| Idempotence :    | $x \wedge x$            |   |                                       |

|------------------|-------------------------|---|---------------------------------------|

|                  | $x \lor x$              | = | x                                     |

| Absorption :     | $x \wedge ( x ee y)$    | = | $oldsymbol{x}$                        |

|                  | $x ee (x \wedge y)$     |   |                                       |

| Distributivity : |                         |   |                                       |

|                  | $x ee$ ( $y \wedge z$ ) | = | ( $x \lor y$ ) $\land$ ( $x \lor z$ ) |

| Annihilation :   |                         |   |                                       |

|                  | $x ee \mathtt{1}$       | = | 1                                     |

Complementation :

Double negation :

$\neg \neg x = x$

De Morgan duality :

$$\neg x \land \neg y = \neg (x \lor y)$$

$$\neg x \lor \neg y = \neg (x \land y)$$

$$\neg 1 = 0$$

$$\neg 0 = 1$$

#### Definition

A boolean algebra is defined as a set **A** equipped with the operations and constants  $\land \lor \neg o \mathbf{1}$  satisfying the mentioned equations.

**Observation :** every boolean algebra is ordered by the order below :

In this ordered set **A** :

- the constant o is the least element

- the constant 1 is the greatest element

Recall that an order is a transitive, reflexive and antisymmetric relation.

Moreover, the two operations  $\land \lor$  are monotone in the sense that :  $\forall x, x', y, y' \in A \times A \times A$   $x \leq x'$  and  $y \leq y' \Rightarrow x \land y \leq x' \land y'$  $x \leq x'$  and  $y \leq y' \Rightarrow x \lor y \leq x' \lor y'$

Accordingly, the negation  $\neg$  is anti-monotone in the sense that :

### **Example of boolean algebra**

The set **A** = { **true** , **false** } defines a boolean algebra with :

| true $\wedge$ true = true   | true $\lor$ true = true    |

|-----------------------------|----------------------------|

| true $\land$ false = false  | true $\lor$ false = true   |

| false $\land$ false = false | false $\lor$ false = false |

| $\neg$ true = false         | $\neg$ false = true        |

| 1 = true                    | o = false                  |

Observe that in this boolean algebra :

$false = false \land true$

and thus :

false

$$\leq$$

true

### **Example of boolean algebra**

Here, we suppose given a set **U**.

The set **A** whose elements are the subsets of **U** is a boolean algebra with conjunction, disjunction and negation defined as follows :

$X \land Y = X \cap Y \qquad X \lor Y = X \cup Y$  $\neg X = U \setminus X$  $1 = U \qquad o = \emptyset$

Observe that one recovers the boolean algebra { true , false } when **U** is defined as the singleton set  $\mathbf{U} = \{*\}$ .

true =

$$\{*\}$$

false =  $\emptyset$

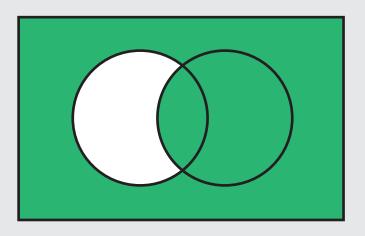

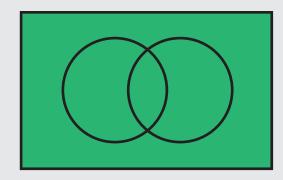

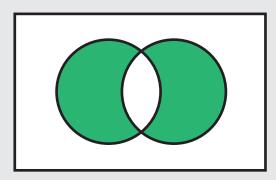

### Venn diagrams

1 = U

$$o = \emptyset$$

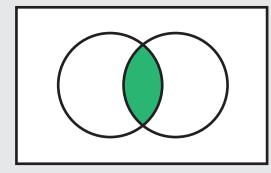

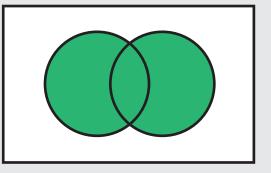

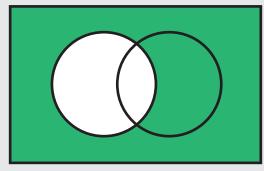

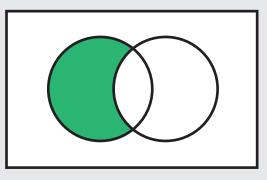

$X \land Y = X \cap Y$

$$X \lor Y = X \cup Y$$

$\neg X = U \setminus X$

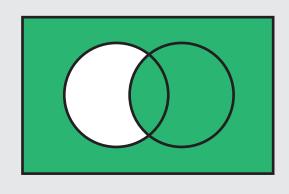

### Venn diagrams ( derived constructions )

Difference

$$X \setminus Y = X \land \neg Y$$

Symmetric difference

= exclusive or

# $\begin{array}{rcl} X \bigtriangleup Y &=& (X \lor Y) \land (X \land Y) \\ &=& (X \lor Y) \land \neg (X \land Y) \end{array}$

### Venn diagrams ( derived constructions )

Implication

$$\begin{array}{rcl} \mathsf{X} \longrightarrow \mathsf{Y} &=& \neg ( \mathsf{X} \land \neg \mathsf{Y} ) \\ &=& \neg \mathsf{X} & \lor & \mathsf{Y} \end{array}$$

Key property of implication :

$$X \leq Y \rightarrow Z \quad \Leftrightarrow \quad X \wedge Y \leq Z$$

### **Product-of-sums form**

Every boolean expression may be transformed modulo the equations of boolean algebras into a conjunction of disjunctions :

| prodofsum | = | 1   sum   prodofsum $\land$ prodofsum |

|-----------|---|---------------------------------------|

| sum       | = | o   literal   sum $\lor$ sum          |

| literal   | = | atom   ¬ atom                         |

Same grammar formulated this time with the arithmetic notation :

| prodofsum | = | 1   sum   prodofsum x prodofsum |

|-----------|---|---------------------------------|

| sum       | = | o   literal   sum + sum         |

| literal   | = | atom   atom                     |

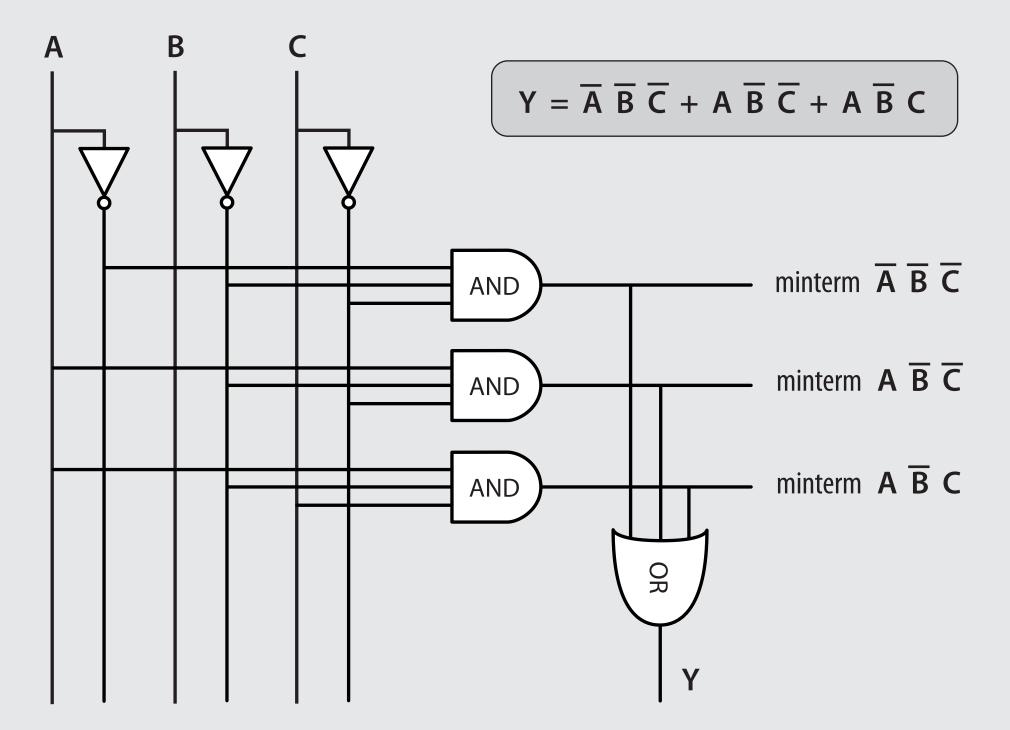

### Sum-of-products form

Every boolean expression may be transformed modulo the equations of boolean algebras into a disjunction of conjunctions :

| sumofprod | = | 0    | prod   sumofprod ∨ sumofprod |

|-----------|---|------|------------------------------|

| prod      | = | 1    | literal   prod $\wedge$ prod |

| literal   | = | atom | ¬ atom                       |

Same grammar formulated this time with the arithmetic notation :

| sumofprod | = | o   prod   sumofprod + sumofprod |

|-----------|---|----------------------------------|

| prod      | = | 1   literal   prod x prod        |

| literal   | = | atom   atom                      |

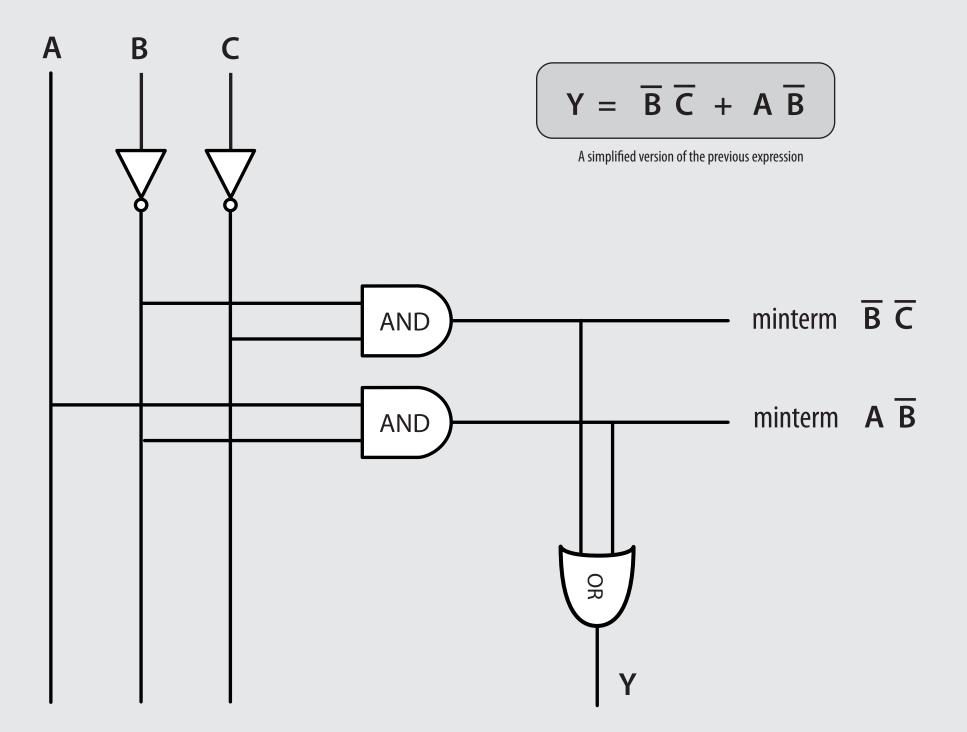

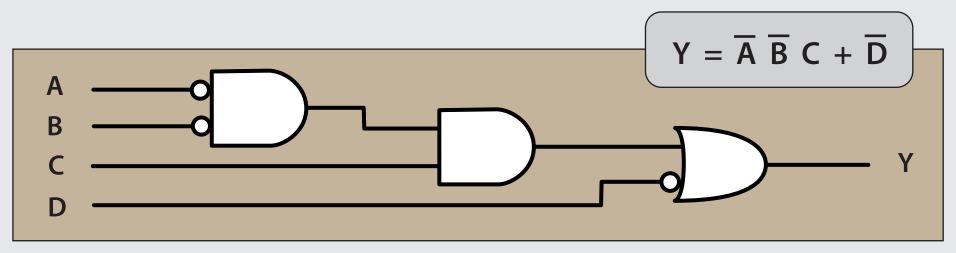

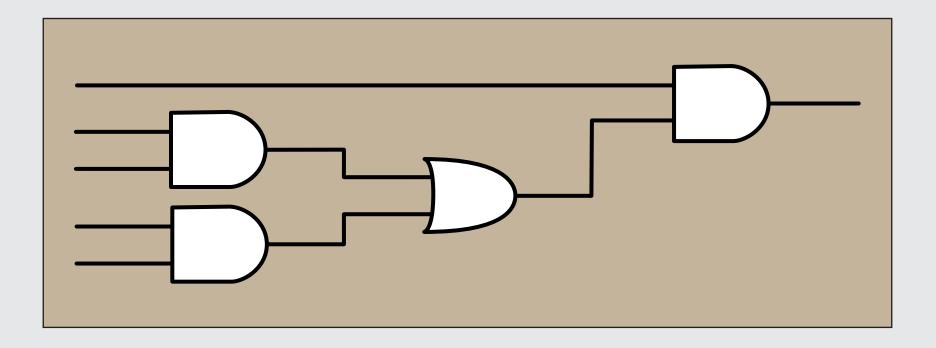

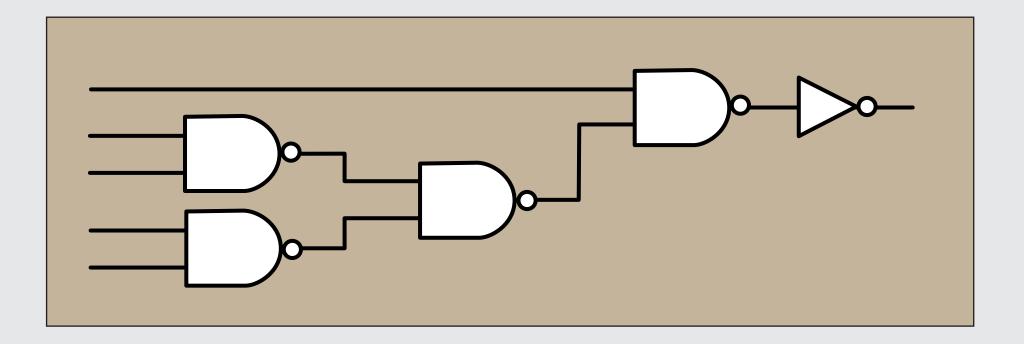

### Sum of products in schematics

### Sum of products in schematics

### Exercise

Show that the equality

#### $\overline{A} \overline{B} \overline{C} + A \overline{B} \overline{C} + A \overline{B} C = \overline{B} \overline{C} + A \overline{B}$

follows from the equations of boolean algebra.

### **Solution**

Show that the equality

$$\overline{A} \overline{B} \overline{C} + A \overline{B} \overline{C} + A \overline{B} C = \overline{B} \overline{C} + A \overline{B}$$

follows from the equations of boolean algebra.

| $\overline{A} \overline{B} \overline{C} + A \overline{B} \overline{C}$ | = | $(A + \overline{A})\overline{B}\overline{C}$ | distributivity  |

|------------------------------------------------------------------------|---|----------------------------------------------|-----------------|

|                                                                        | = | ı B C                                        | complementation |

|                                                                        | = | BC                                           | identity        |

| $A \overline{B} \overline{C} + A \overline{B} C$                       | = | $A\overline{B}(C+\overline{C})$              | distributivity  |

|                                                                        | = | AB1                                          | complementation |

|                                                                        | = | AB                                           | identity        |

### Solution

Show that the equality

$$\overline{A} \overline{B} \overline{C} + A \overline{B} \overline{C} + A \overline{B} C = \overline{B} \overline{C} + A \overline{B}$$

follows from the equations of boolean algebra.

$\overline{A} \ \overline{B} \ \overline{C} + A \ \overline{B} \ \overline{C} + A \ \overline{B} \ \overline{C} = \overline{A} \ \overline{B} \ \overline{C} + A \ \overline{B} \ \overline{C} + A \ \overline{B} \ \overline{C} + A \ \overline{B} \ \overline{C}$ by idempotence and associativity  $= \overline{B} \ \overline{C} + A \ \overline{B}$ by the two equations of the previous page

This establishes the expected equation.

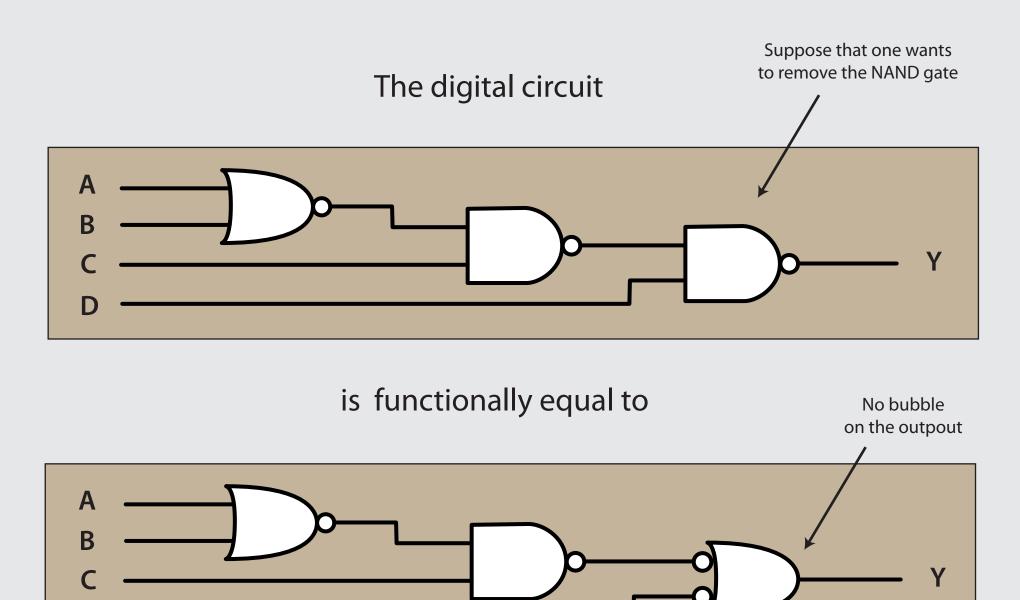

### **Bubble Pushing**

D

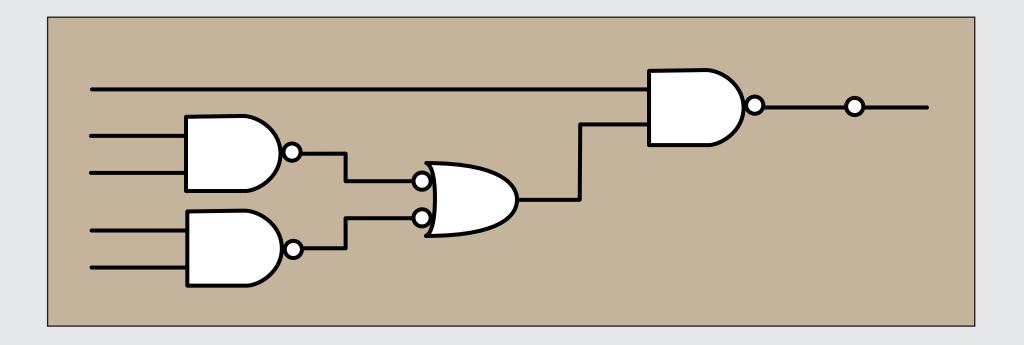

### **Bubble Pushing**

is functionally equal to

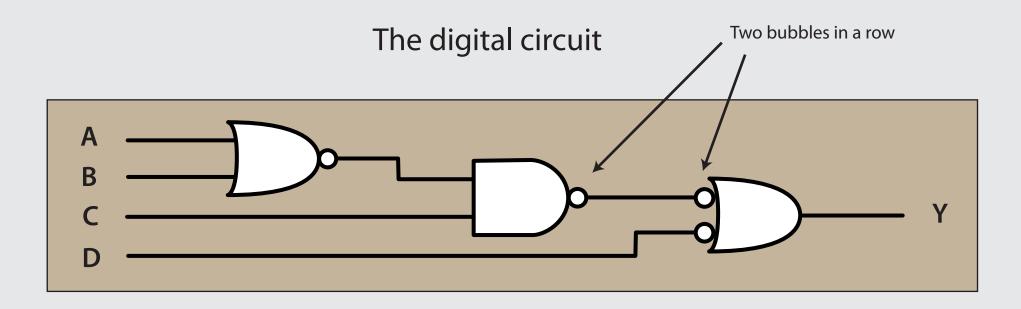

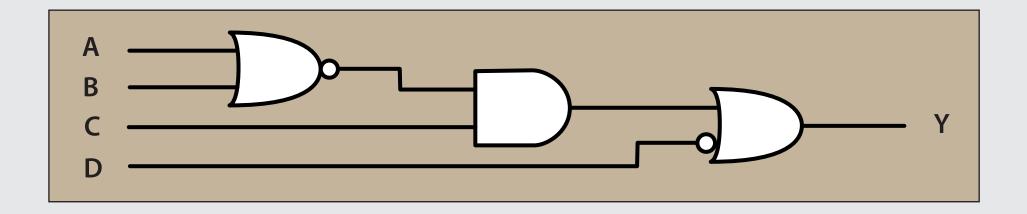

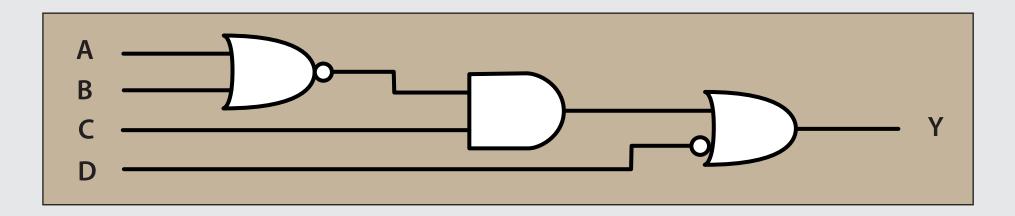

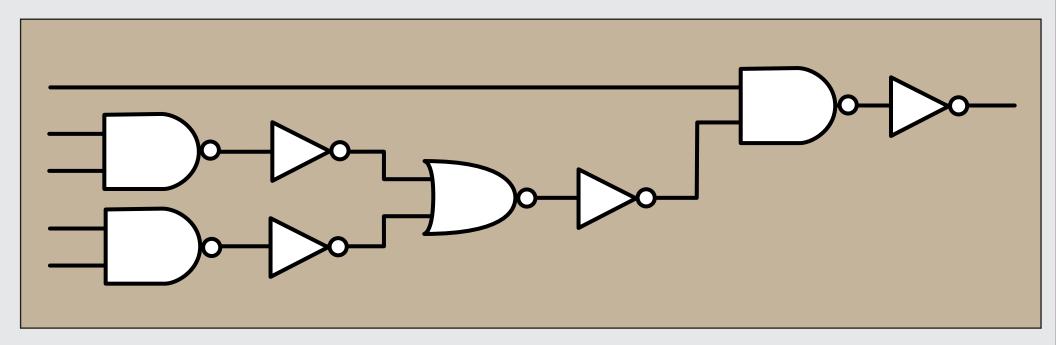

### **Bubble Pushing**

The digital circuit

is functionally equal to

In some situations, one would like to transform a logical circuit expressed with AND and OR gates into an equivalent logical circuit constructed with NAND gates, NOR gates and inverters.

One typical reason is that NAND gates, NOR gates and inverters are easier to construct in CMOS technology.

One brutal way to achieve the translation is to replace

- every AND gate by a NAND gate followed by an inverter

- every OR gate by a NOR gate followed by an inverter

in the way done below :

This procedure works but is far from optimal in general in the number of logical gates in the final CMOS circuit.

A more sophisticated way to achieve the translation is to add two negations on some of the wires of the original logical circuit :

Note that each negation is represented here by a bubble.

A more sophisticated way to achieve the translation is to add two negations on some of the wires of the original logical circuit :

One obtains in this way a CMOS circuit with five logical gates (instead of six gates as in the previous translation)

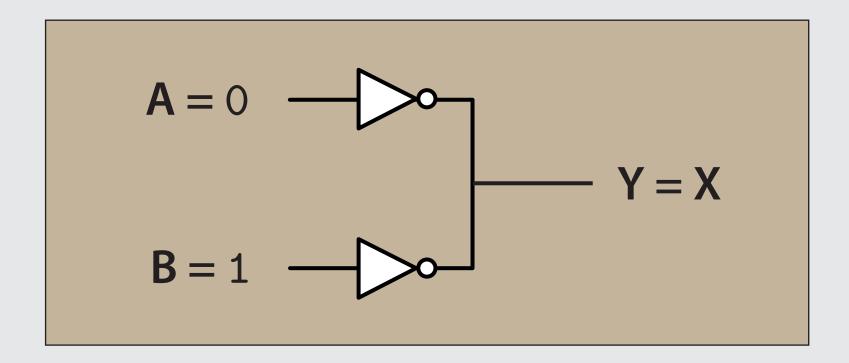

### The illegal value X

Here, the output **Y** has an unknown or illegal value.

The situation is called a « contention » and is considered as an error which should be avoided.

The reason is that contention may cause large amounts of power to be dissipated between the logical gates, resulting in the circuit getting hot and possibly damaged.

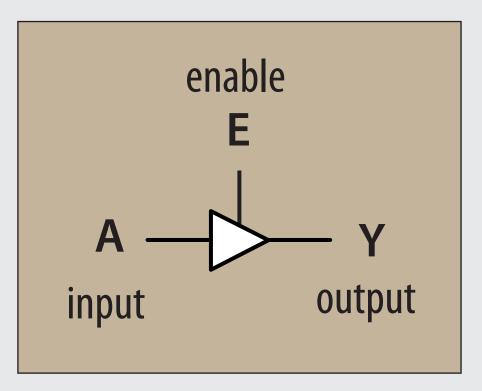

### The floating value Z

| E | А | Y |

|---|---|---|

| 0 | 0 | Z |

| 0 | 1 | Z |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

active high enable

The tristate buffer has three possible output values :

- HIGH (1)

- LOW (0)

- FLOATING (Z)

The output has a floating value means that the wire **Y** may receive any voltage depending on the context.

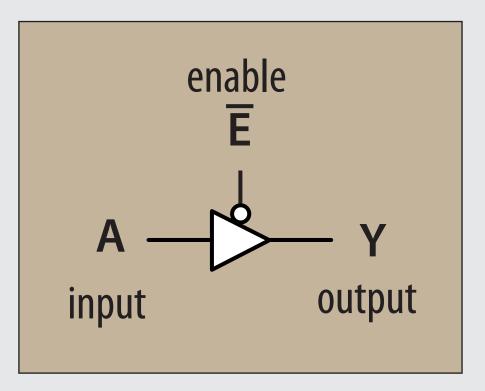

### The floating value Z

| Ē | А | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | Z |

| 1 | 1 | Z |

active low enable

The tristate buffer has three possible output values :

- HIGH (1)

- LOW (0)

- FLOATING (Z)

The output has a floating value means that the wire **Y** may receive any voltage depending on the context.

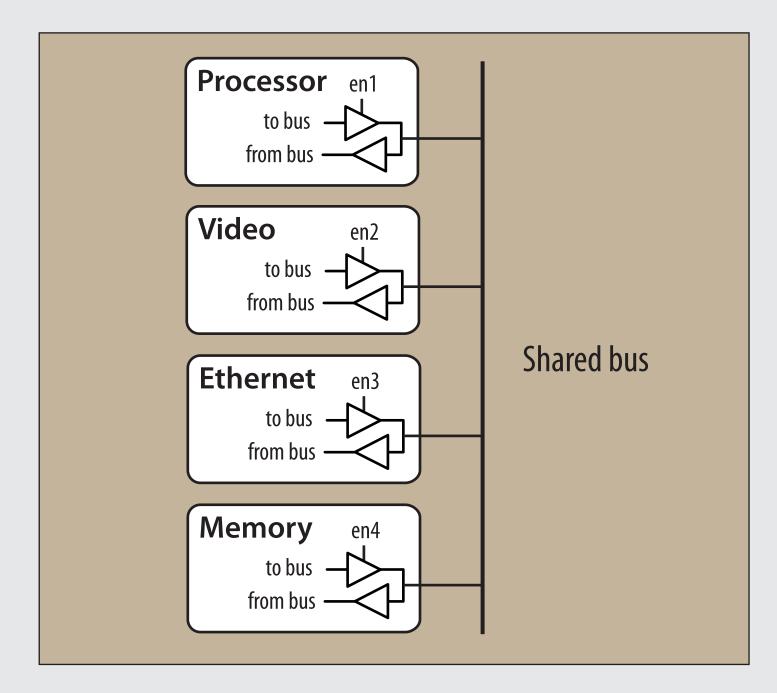

### Tristate bus connecting multiple chips

Today, higher speeds are achieved by point-to-point links between chips

# Karnaugh Maps

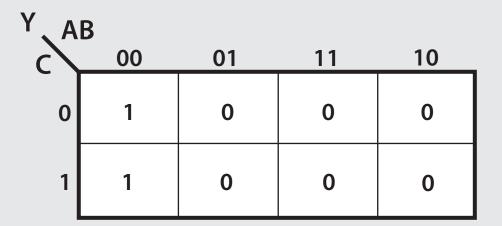

### A typical truth value table

| A | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

### From the truth table to the K-map

| А | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

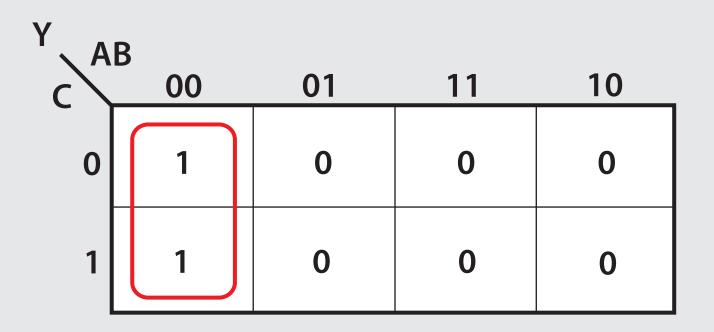

| Y<br>C | B<br>00 | 01 | 11 | 10 |

|--------|---------|----|----|----|

| 0      | 1       | 0  | 0  | 0  |

| 1      | 1       | 0  | 0  | 0  |

Note the clever use of Gray codes here

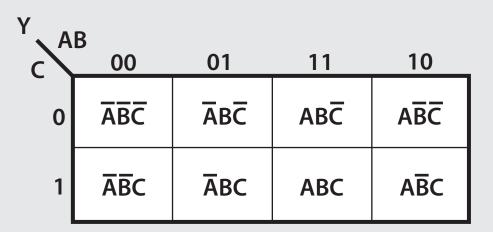

### Same K-map with associated minterms

From this, one deduces that :

$$\left( Y = \overline{A}\overline{B}\overline{C} + \overline{A}\overline{B}C \right)$$

#### **K-map minimisation**

By circling the 1's in adjacent squares, one deduces that :

$$Y = \overline{A}\overline{B}\overline{C} + \overline{A}\overline{B}C = \overline{A}\overline{B}$$

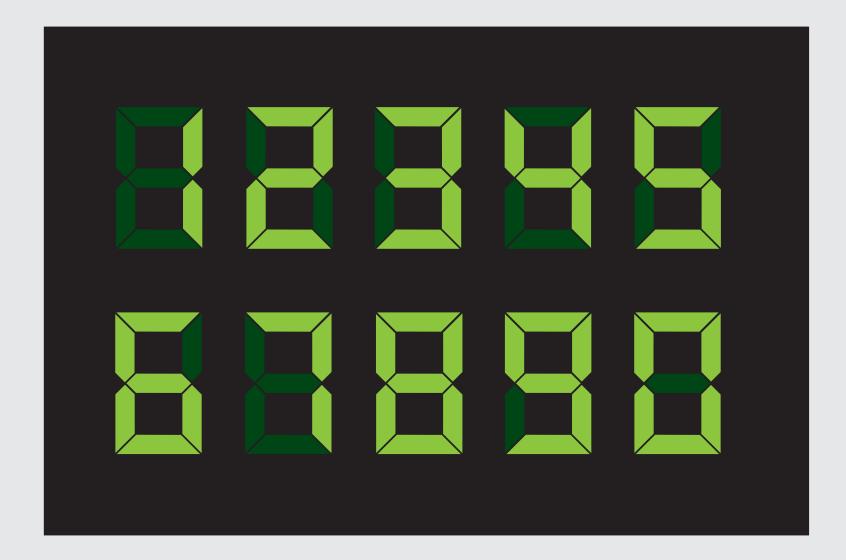

#### Seven-segment display digits

Seven-segment display digits were invented at the beginning of the 20th century. They became very popular in the 1970's with the advent of LED.

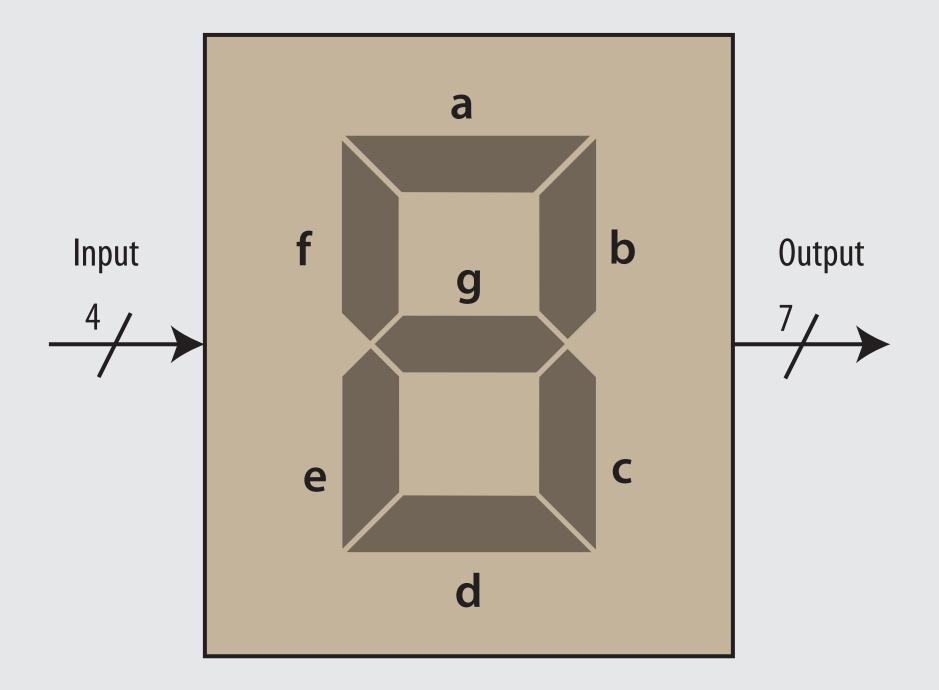

#### Seven-segment display decoder

#### Seven-segment display decoder truth table

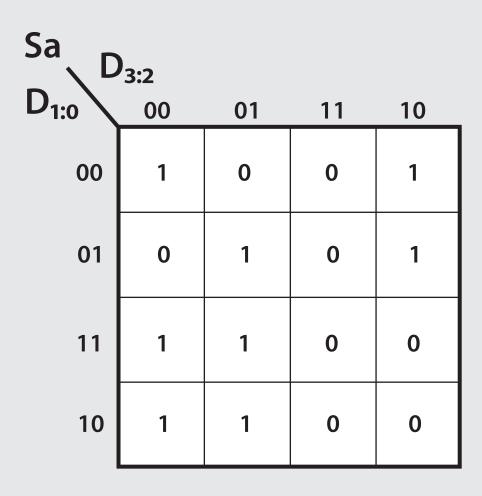

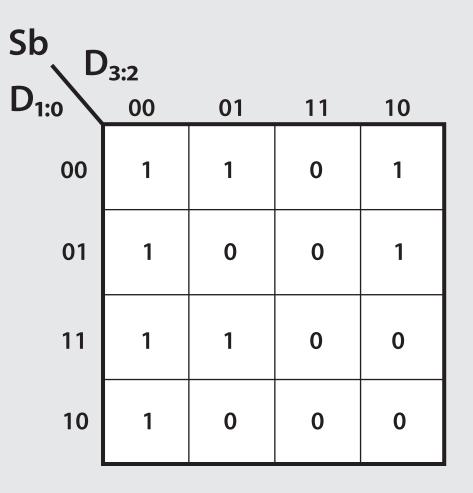

| D <sub>3:0</sub> | Sa | Sb | Sc | Sd | Se | Sf | Sg |

|------------------|----|----|----|----|----|----|----|

| 0000             | 1  | 1  | 1  | 1  | 1  | 1  | 0  |

| 0001             | 0  | 1  | 1  | 0  | 0  | 0  | 0  |

| 0010             | 1  | 1  | 0  | 1  | 1  | 0  | 1  |

| 0011             | 1  | 1  | 1  | 1  | 0  | 0  | 1  |

| 0100             | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

| 0101             | 1  | 0  | 1  | 1  | 0  | 1  | 1  |

| 0110             | 1  | 0  | 1  | 1  | 1  | 1  | 1  |

| 0111             | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

| 1000             | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 1001             | 1  | 1  | 1  | 1  | 0  | 1  | 1  |

| others           | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

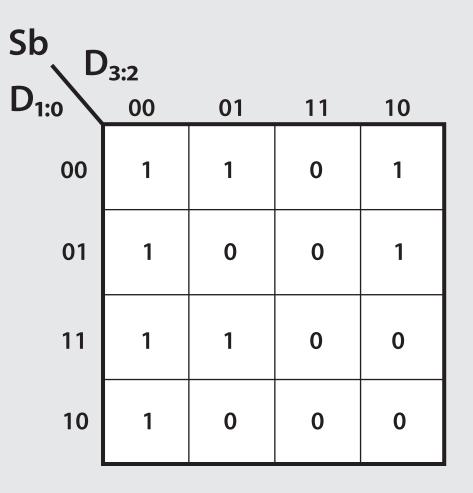

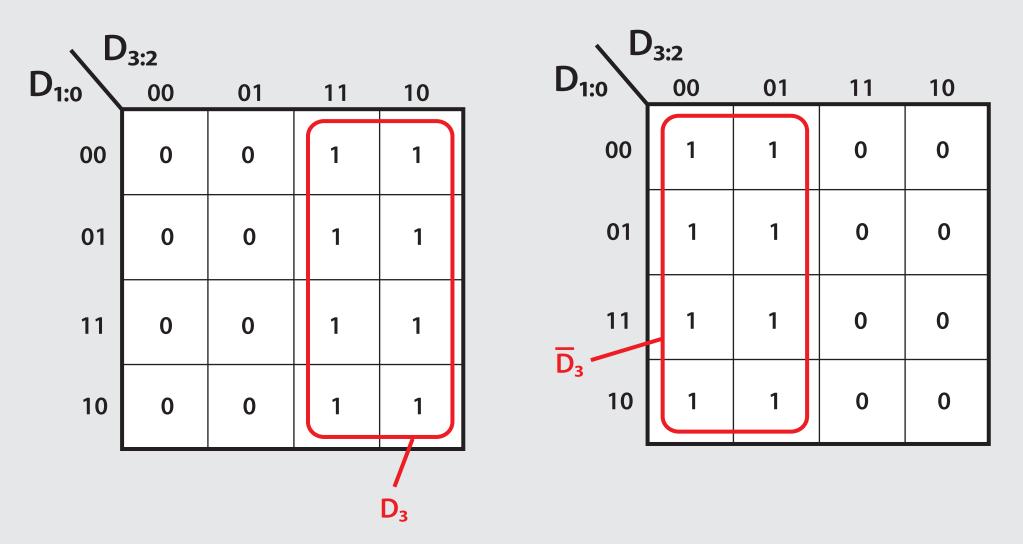

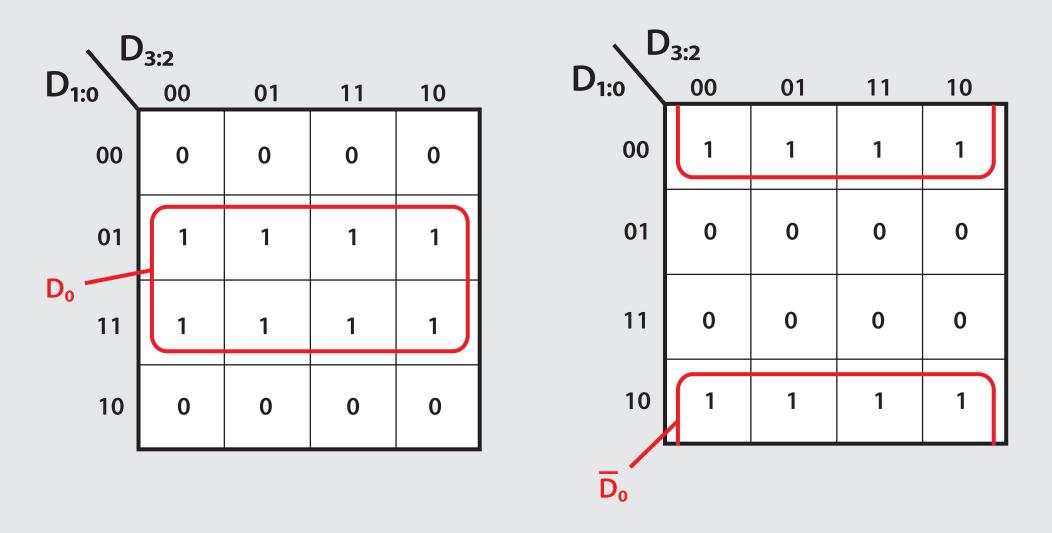

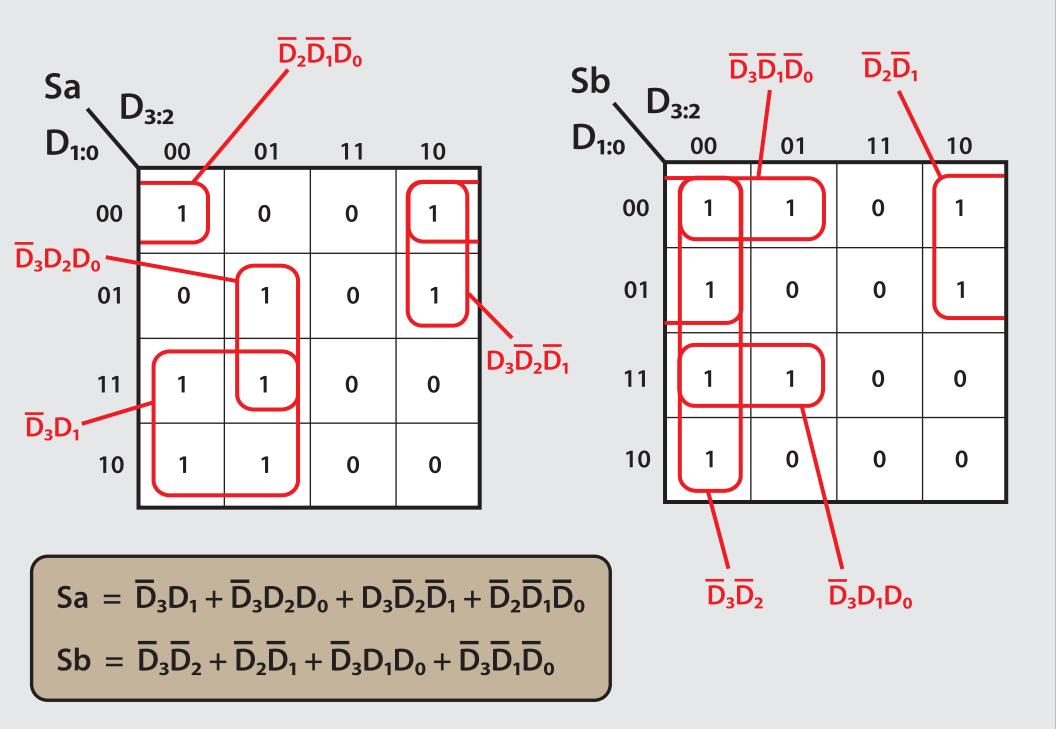

$D_3$  denotes the set of inputs with input bit  $D_3$  equal to 1  $\overline{D}_3$  denotes the set of inputs with input bit  $D_3$  equal to 0

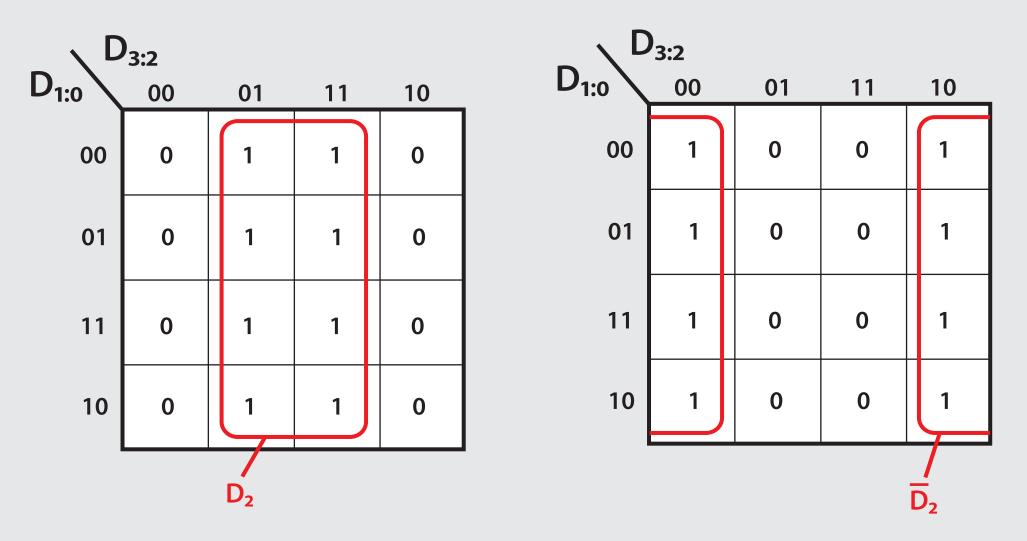

$D_2$  denotes the set of inputs with input bit  $D_2$  equal to 1  $\overline{D}_2$  denotes the set of inputs with input bit  $D_2$  equal to 0

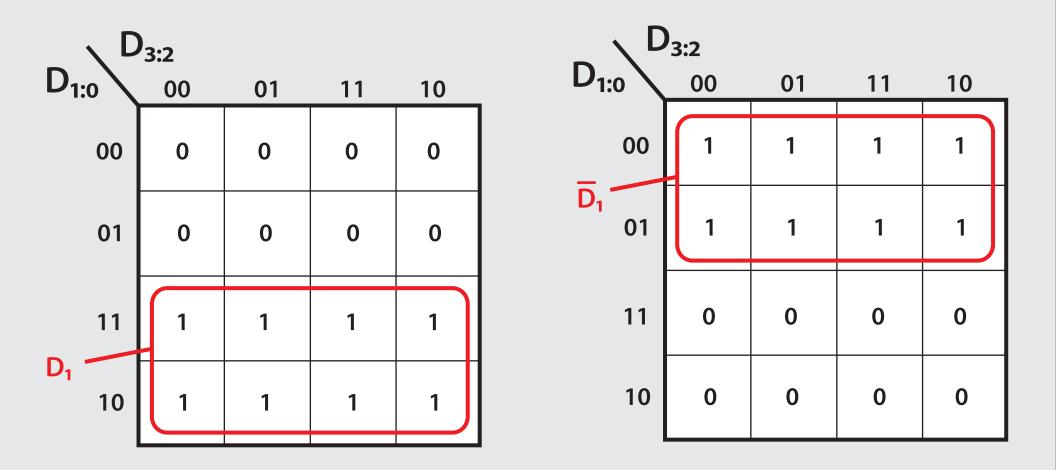

$D_1$  denotes the set of inputs with input bit  $D_1$  equal to 1  $\overline{D}_1$  denotes the set of inputs with input bit  $D_1$  equal to 0

$D_0$  denotes the set of inputs with input bit  $D_0$  equal to 1  $\overline{D}_0$  denotes the set of inputs with input bit  $D_0$  equal to 0

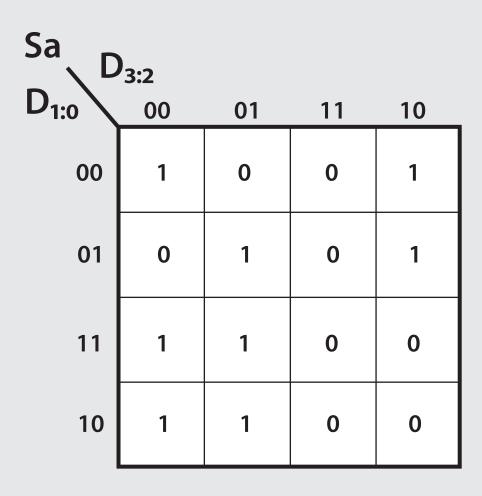

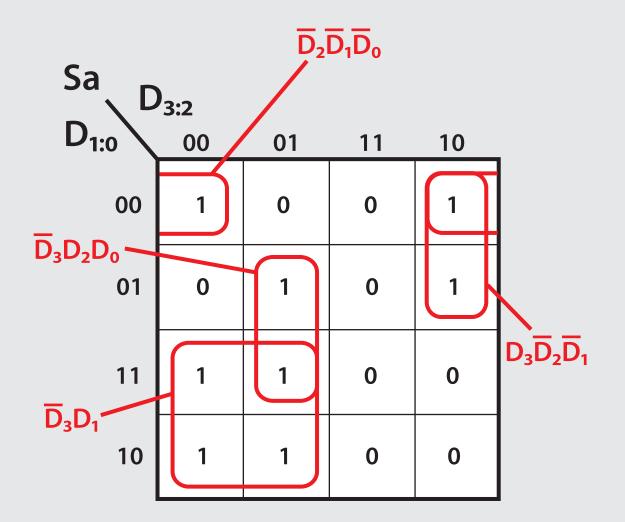

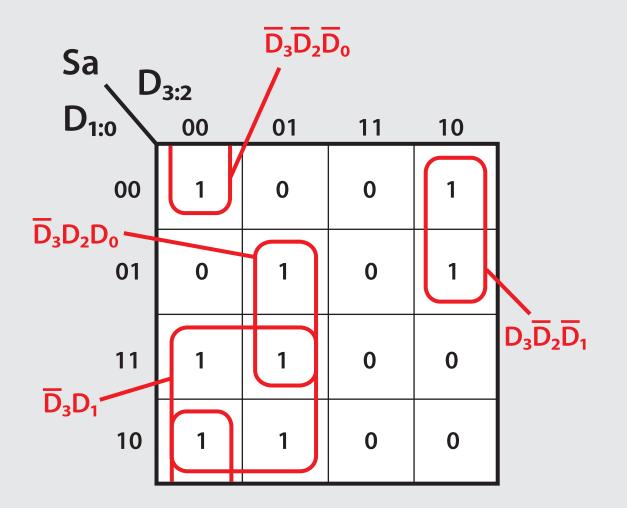

Sa =  $\overline{D}_3D_1 + \overline{D}_3D_2D_0 + D_3\overline{D}_2\overline{D}_1 + \overline{D}_2\overline{D}_1\overline{D}_0$

Sa =  $\overline{D}_3D_1 + \overline{D}_3D_2D_0 + D_3\overline{D}_2\overline{D}_1 + \overline{D}_3\overline{D}_2\overline{D}_0$

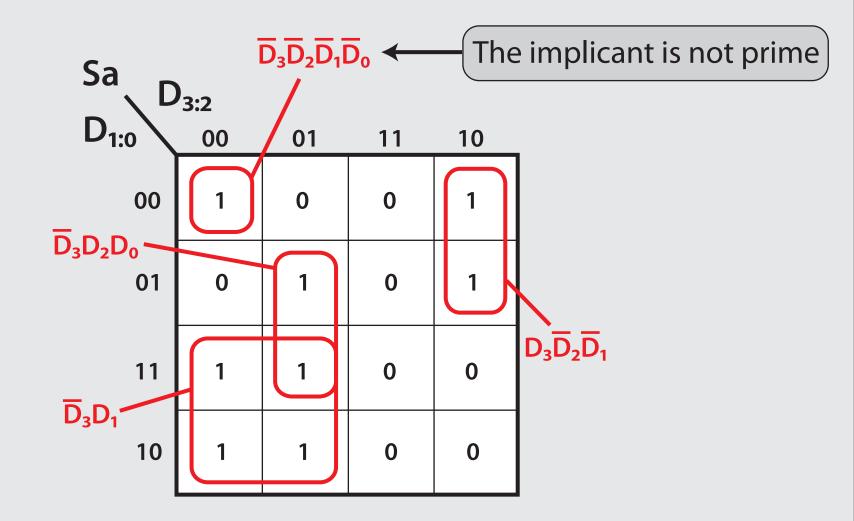

#### A common mistake

Sa =  $\overline{D}_3D_1 + \overline{D}_3D_2D_0 + D_3\overline{D}_2\overline{D}_1 + \overline{D}_3\overline{D}_2\overline{D}_1\overline{D}_0$

# Seven-segment display decoder truth table with X's

| D <sub>3:0</sub> | Sa | Sb | Sc | Sd | Se | Sf | Sg |

|------------------|----|----|----|----|----|----|----|

| 0000             | 1  | 1  | 1  | 1  | 1  | 1  | 0  |

| 0001             | 0  | 1  | 1  | 0  | 0  | 0  | 0  |

| 0010             | 1  | 1  | 0  | 1  | 1  | 0  | 1  |

| 0011             | 1  | 1  | 1  | 1  | 0  | 0  | 1  |

| 0100             | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

| 0101             | 1  | 0  | 1  | 1  | 0  | 1  | 1  |

| 0110             | 1  | 0  | 1  | 1  | 1  | 1  | 1  |

| 0111             | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

| 1000             | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 1001             | 1  | 1  | 1  | 1  | 0  | 1  | 1  |

| others           | X  | X  | X  | X  | X  | Х  | X  |

Here, the value **X** means that the value is undetermined : it can be 0 or 1.

#### **Decoder K-maps minimisation with X's**

## **Exercise** 1

Complete the design of the seven-segment decoder by designing boolean equations for the segments Sc and Sd :

- a. assuming that inputs greater than 9 must produce blank (0) outputs

- b. assuming that inputs greater than 9 are don't cares

Then, sketch a reasonably simple gate-level implementation in the case b. and simulate the resulting circuits on CircuitLab.

## **Combinational Building Blocks**

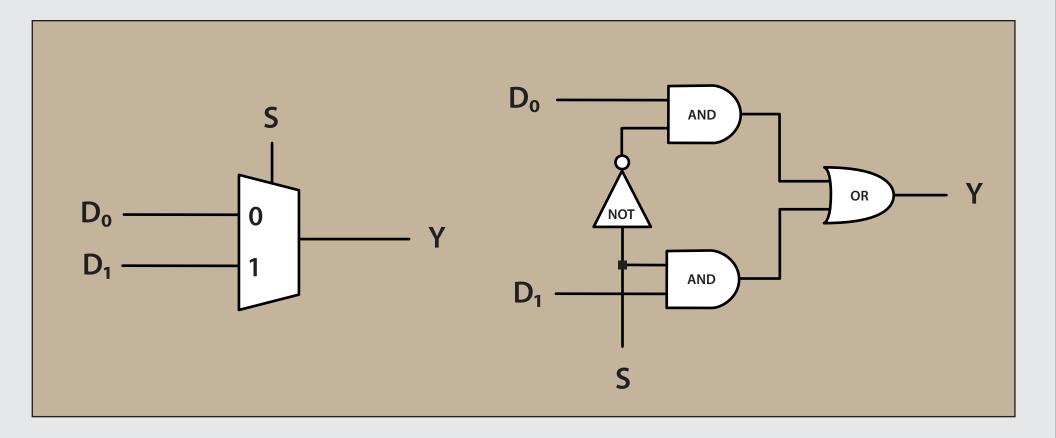

#### Multiplexor (mux)

| S | Y              |

|---|----------------|

| 0 | Do             |

| 1 | D <sub>1</sub> |

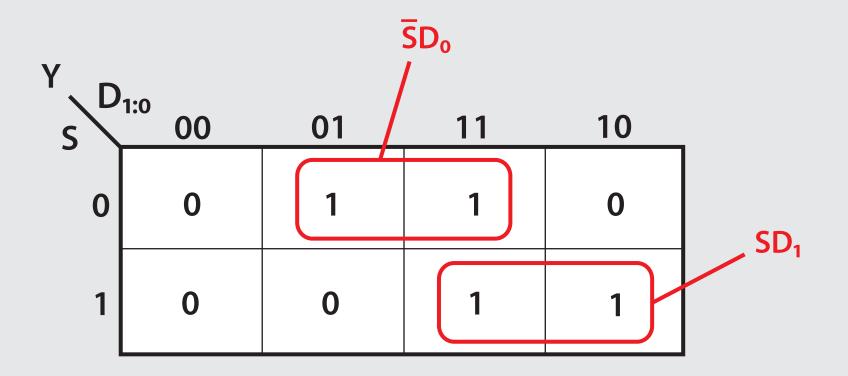

#### **K-map minimisation**

By circling the 1's in adjacent squares, one deduces that :

$$\left( \begin{array}{c} Y = SD_1 + \overline{S}D_0 \end{array} \right)$$

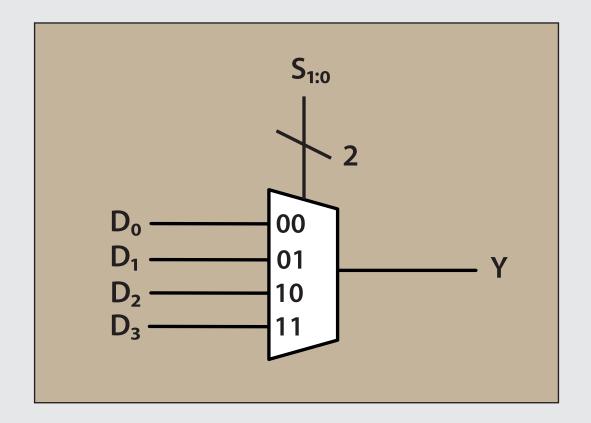

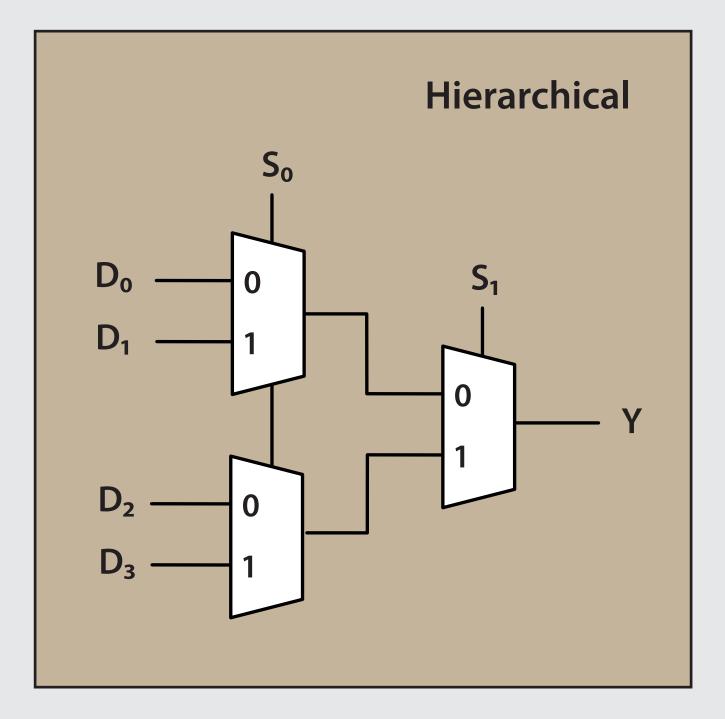

#### 4:1 multiplexers

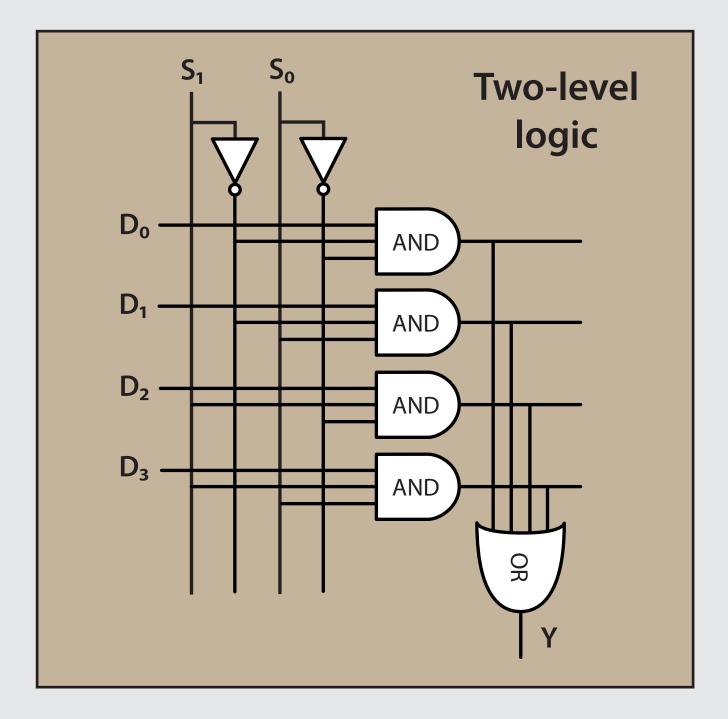

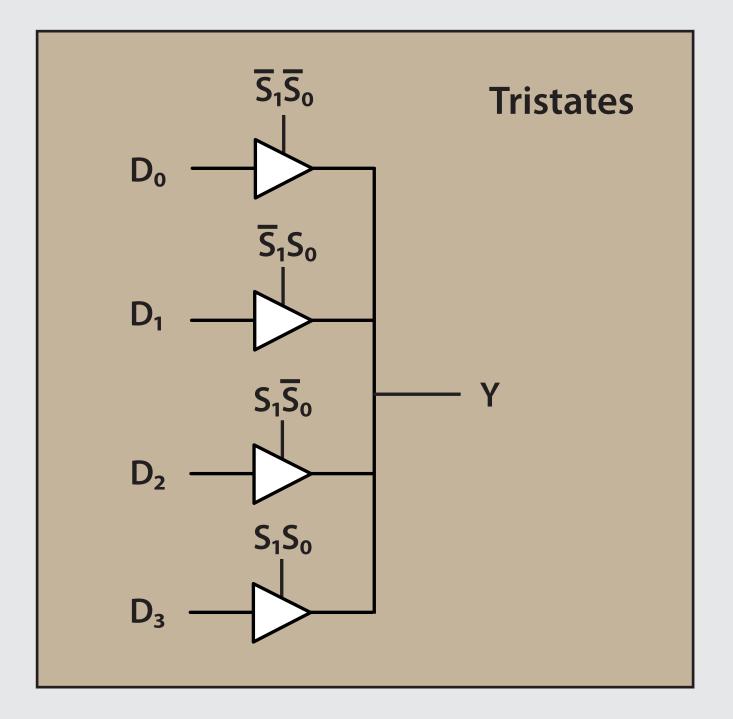

#### Implementation of the 4:1 multiplexer

#### Implementation of the 4:1 multiplexer

#### Implementation of the 4:1 multiplexer

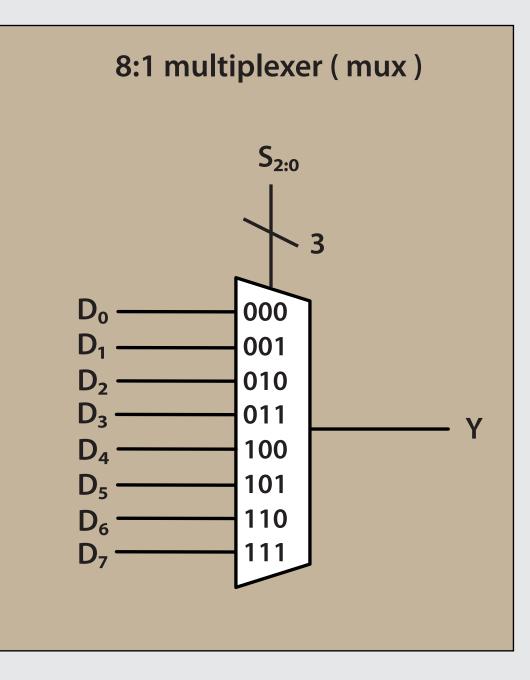

#### Exercise

Alyssa P. Hacker needs to implement the function

#### $Y = A\overline{B} + \overline{B}\overline{C} + \overline{A}BC$

to finish her senior project, but when she looks in her lab kit, the only part she has left is an 8:1 multiplexer.

How does she implement the function?

#### **Solution**

$$Y = A\overline{B} + \overline{B}\overline{C} + \overline{A}BC$$

| А | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

**Solution**

$$Y = A\overline{B} + \overline{B}\overline{C} + \overline{A}BC$$

| А | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

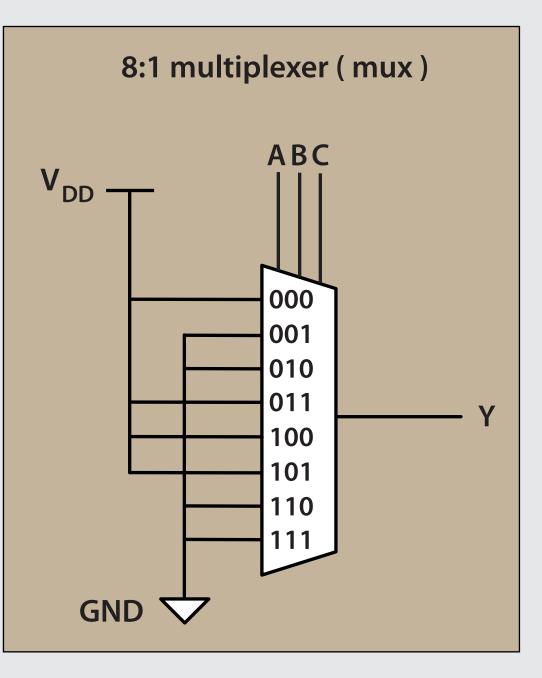

#### Exercise

Can you construct the same boolean function with a 4:1 multiplexer and an inverter ?

| <b>Y</b> = | AB + | BC + A | BC | 4:1 multiplexer ( mux )<br>S <sub>1:0</sub>          |

|------------|------|--------|----|------------------------------------------------------|

| A          | В    | С      | Y  |                                                      |

| 0          | 0    | 0      | 1  | 2                                                    |

| 0          | 0    | 1      | 0  | $D_0 \longrightarrow 00$                             |

| 0          | 1    | 0      | 0  | D <sub>1</sub> 01 Y                                  |

| 0          | 1    | 1      | 1  | $D_2 \longrightarrow 10$<br>$D_3 \longrightarrow 11$ |

| 1          | 0    | 0      | 1  |                                                      |

| 1          | 0    | 1      | 1  | inverter                                             |

| 1          | 1    | 0      | 0  |                                                      |

| 1          | 1    | 1      | 0  |                                                      |

#### Solution

Can you construct the same boolean function with a 4:1 multiplexer and an inverter ?

| AB                                                                                                                 | $Y = A\overline{B} + \overline{B}\overline{C} + \overline{A}BC$ |   |   |   |  |  |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---|---|---|--|--|

|                                                                                                                    | Y                                                               | С | В | Α |  |  |

|                                                                                                                    | 1                                                               | 0 | 0 | 0 |  |  |

|                                                                                                                    | 0                                                               | 1 | 0 | 0 |  |  |

| $\begin{array}{c c} C & \hline & V_{DD} & \hline & 01 \\ \hline & V_{DD} & \hline & 10 \\ \hline & 10 \end{array}$ | 0                                                               | 0 | 1 | 0 |  |  |

|                                                                                                                    | 1                                                               | 1 | 1 | 0 |  |  |

| 11                                                                                                                 | 1                                                               | 0 | 0 | 1 |  |  |

|                                                                                                                    | 1                                                               | 1 | 0 | 1 |  |  |

| GND 🔽                                                                                                              | 0                                                               | 0 | 1 | 1 |  |  |

|                                                                                                                    | 0                                                               | 1 | 1 | 1 |  |  |

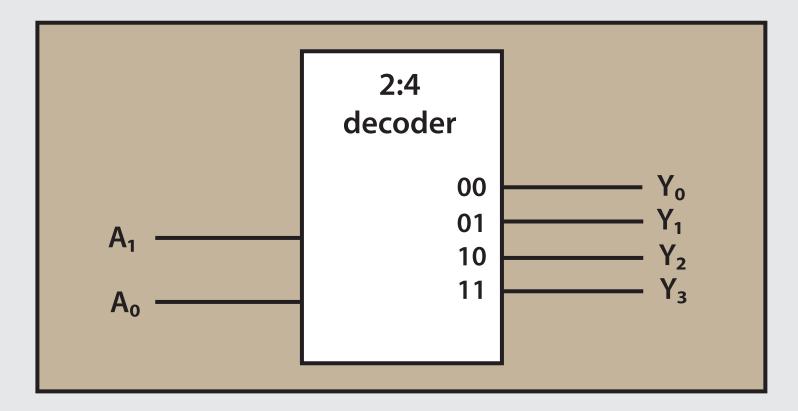

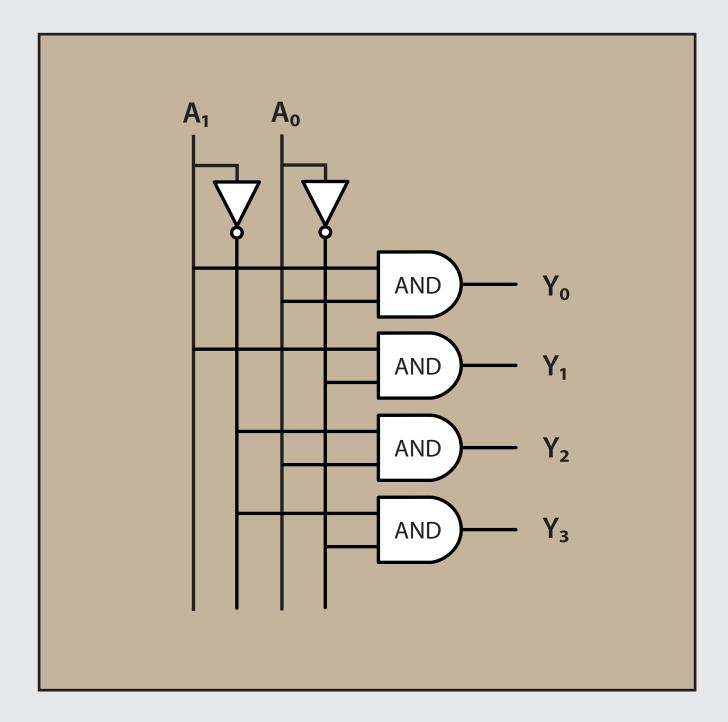

#### Decoders

| A <sub>1</sub> | Ao | Y <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> |

|----------------|----|----------------|----------------|----------------|----------------|

| 0              | 0  | 0              | 0              | 0              | 1              |

| 0              | 1  | 0              | 0              | 1              | 0              |

| 1              | 0  | 0              | 1              | 0              | 0              |

| 1              | 1  | 1              | 0              | 0              | 0              |

#### Implementation of the 2:4 decoder

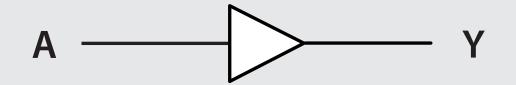

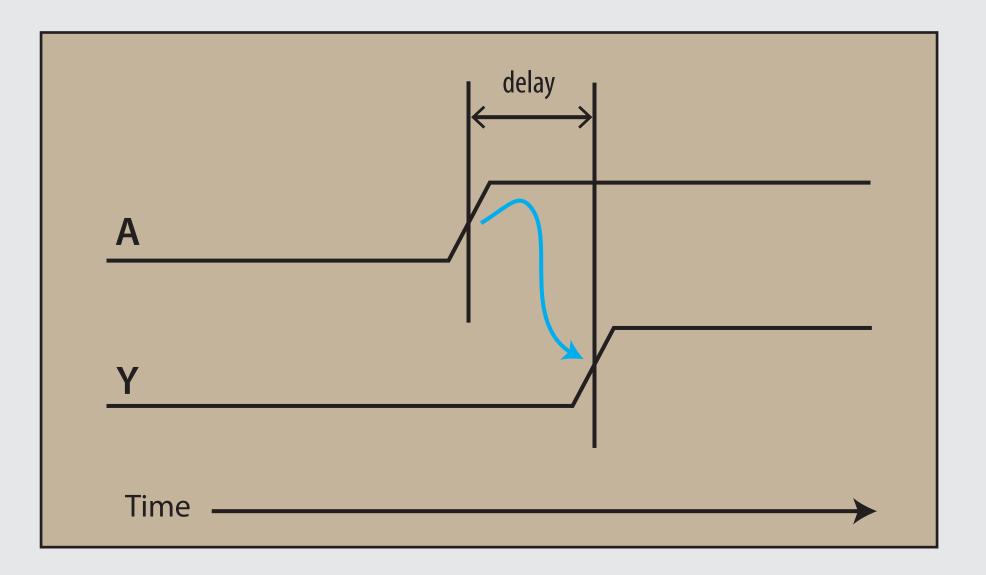

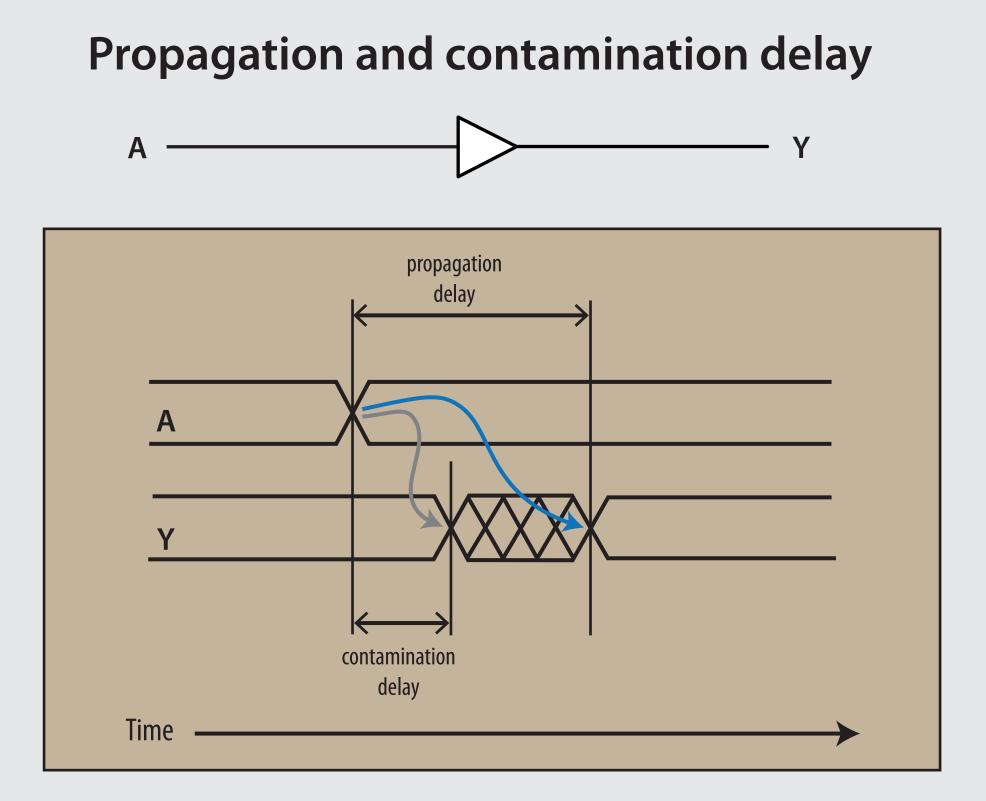

## Timing

#### **Time delay**

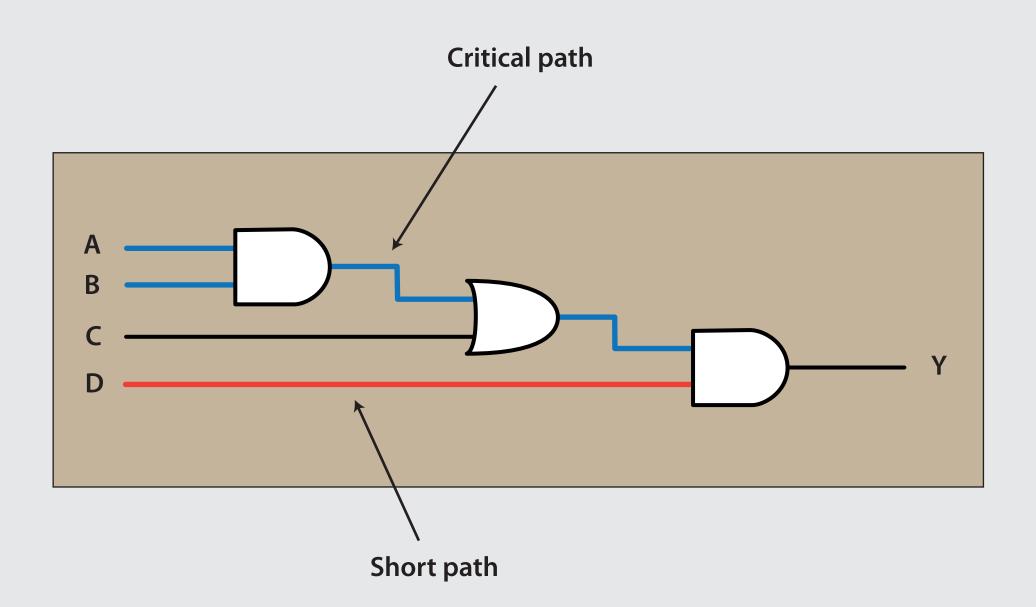

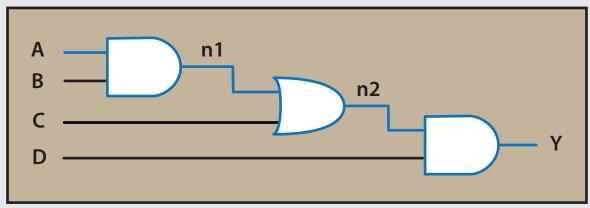

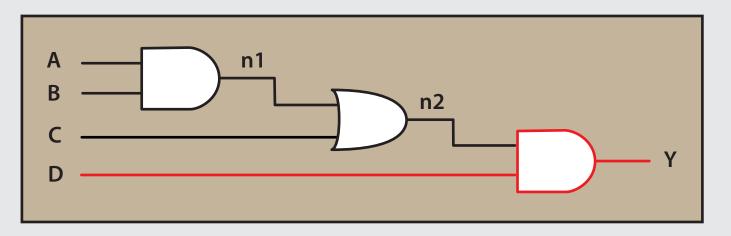

#### **Critical vs. short path**

### Critical path waveform

$$t_{pd} = 2 t_{pd_and} + t_{pd_or}$$

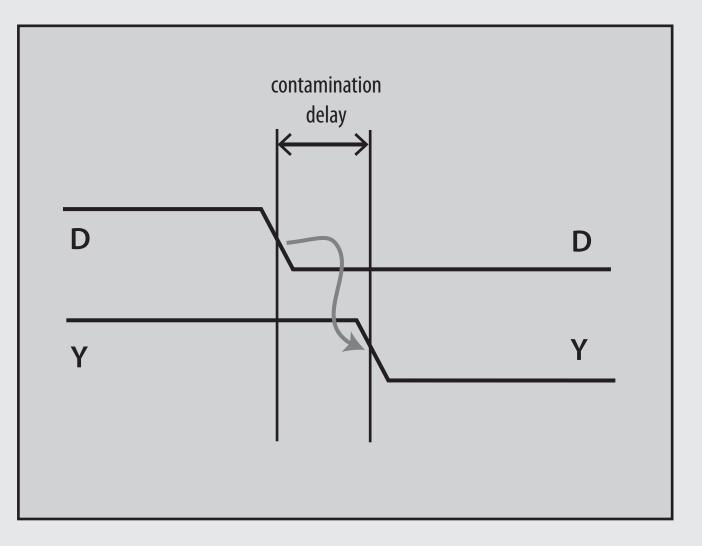

### Short path waveform

## **Exercise 2**

#### H & H Example 2.16

Given the propagation delays for the components given below, compare the worst-case timing of the three four-input multiplexer designs.

What is the critical path for each design?

Given your timing analysis, why might you choose one design over the other?

| Gate                     | t <sub>pd</sub> (ps) |

|--------------------------|----------------------|

| NOT                      | 30                   |

| 2-input AND              | 60                   |

| 3-input AND              | 80                   |

| 4-input OR               | 90                   |

| tristate ( A to Y )      | 50                   |

| tristate ( enable to Y ) | 35                   |